1. Tujuan [Kembali]

memahami apa itu RAM dan fungsi dari RAM (random access memory).

2. Alat dan bahan [Kembali]

1. cd 4001

2. gerbang nand

3. inverter

4. logic probe

5.logic state

3. Teori [Kembali]

Seperti disebutkan sebelumnya, elemen dasar SRAM adalah sel memori kait. Gambar 15.4 menunjukkan sel memori SRAM dasar. Sel memori dipilih dengan mengatur jalur 'pilih' aktif. Bit data ditulis ke dalam sel dengan menempatkannya di baris 'data in' dan dibaca dari baris 'data out'. SRAM dapat secara luas diklasifikasikan sebagai SRAM asinkron dan SRAM sinkron. SRAM asinkron adalah mereka yang operasinya tidak disinkronkan dengan jam sistem, yaitu mereka beroperasi secara independen dari frekuensi jam. 'Data masuk' dan 'data keluar' dalam RAM ini dikendalikan oleh transisi alamat. SRAM sinkron adalah mereka yang timingnya dimulai oleh ujung jam. 'Alamat', 'data masuk', 'data keluar' dan semua sinyal kontrol lainnya disinkronkan dengan sinyal jam. Sinkronis

SRAM biasanya memiliki fitur burst alamat, yang memungkinkan memori untuk membaca dan menulis di lebih dari satu lokasi menggunakan satu alamat. SRAMs sinkron dan asinkron tersedia dalam teknologi bipolar, MOS dan BiCMOS . Sementara SRAM bipolar menawarkan kecepatan operasi yang relatif lebih tinggi, teknologi MOS menawarkan kapasitas yang lebih tinggi dan konsumsi daya yang berkurang.

RAM Statis

Seperti disebutkan sebelumnya, elemen dasar SRAM adalah sel memori kait. Gambar 15.4 menunjukkan sel memori SRAM dasar. Sel memori dipilih dengan mengatur jalur 'pilih' aktif. Bit data ditulis ke dalam sel dengan menempatkannya di baris 'data in' dan dibaca dari baris 'data out'. SRAM dapat secara luas diklasifikasikan sebagai SRAM asinkron dan SRAM sinkron. SRAM asinkron adalah mereka yang operasinya tidak disinkronkan dengan jam sistem, yaitu mereka beroperasi secara independen dari frekuensi jam. 'Data masuk' dan 'data keluar' dalam RAM ini dikendalikan oleh transisi alamat. SRAM sinkron adalah mereka yang timingnya dimulai oleh ujung jam. 'Alamat', 'data masuk', 'data keluar' dan semua sinyal kontrol lainnya disinkronkan dengan sinyal jam. Sinkronis

SRAM biasanya memiliki fitur burst alamat, yang memungkinkan memori untuk membaca dan menulis di lebih dari satu lokasi menggunakan satu alamat. SRAMs sinkron dan asinkron tersedia dalam teknologi bipolar, MOS dan BiCMOS . Sementara SRAM bipolar menawarkan kecepatan operasi yang relatif lebih tinggi, teknologi MOS menawarkan kapasitas yang lebih tinggi dan konsumsi daya yang berkurang. Gambar 15.5 (a) dan (b) masing-masing menunjukkan sel memori bipolar dasar dan sel memori MOS (NMOS).

SRAM biasanya memiliki fitur burst alamat, yang memungkinkan memori untuk membaca dan menulis di lebih dari satu lokasi menggunakan satu alamat. SRAMs sinkron dan asinkron tersedia dalam teknologi bipolar, MOS dan BiCMOS . Sementara SRAM bipolar menawarkan kecepatan operasi yang relatif lebih tinggi, teknologi MOS menawarkan kapasitas yang lebih tinggi dan konsumsi daya yang berkurang.gambar (a) dan (b) masing-masing menunjukkan sel memori bipolar dasar dan sel memori MOS (NMOS).

SRAM asinkron

gambar diatas menunjukkan arsitektur khas SRAM asinkron 64 × 8. Itu mampu menyimpan 64 kata dari delapan bit masing-masing. Blok utama termasuk decoder alamat baris 6-ke-64, buffer I / O, 64 sel memori dan logika kontrol untuk operasi baca / tulis. Sel memori dalam satu baris direpresentasikan sebagai register. Setiap register adalah register delapan bit dan dapat dibaca dari serta ditulis ke dalamnya. Seperti dapat dilihat dari gambar, semua sel di dalam register yang sama berbagi baris output decoder yang sama, juga disebut sebagai 'baris baris'. Fungsi kontrol disediakan oleh input R / W (baca / tulis) dan CS (pilih chip). Input R / W dan CS juga disebut sebagai input WE (write enable) dan CE (chip enable). Baris 'input data' dan 'output data' biasanya digabungkan dengan menggunakan jalur input / output yang umum untuk menghemat jumlah pin pada paket IC. Memori dipilih dengan membuat CS = 0. Selama operasi 'baca', status pin R / W dan CS masing-masing adalah '1' dan '0', sedangkan selama operasi 'tulis' masing-masing adalah '0' dan '0'. Selama operasi 'baca' buffer input dinonaktifkan dan konten register yang dipilih muncul di output. Selama operasi 'tulis' buffer input diaktifkan dan buffer output dinonaktifkan. Isi buffer input dimuat ke register yang dipilih, data sebelumnya yang ditimpa oleh data baru. Buffer output, sedang tristate , berada dalam keadaan impedansi tinggi selama operasi penulisan. CS = 1 membatalkan pilihan chip, dan input dan output data buffer dinonaktifkan dan pergi ke keadaan impedansi tinggi. Isi memori dalam kasus ini tetap tidak terpengaruh. Input 'chip Select' sangat penting ketika lebih dari satu chip memori RAM digabungkan untuk mendapatkan kapasitas memori yang lebih besar. Dalam kasus memori SRAM yang lebih besar, ada dua decoder alamat, satu untuk baris dan satu untuk kolom. Mereka disebut sebagai decoder baris dan decoder kolom masing-masing. Beberapa baris alamat diumpankan ke dekoder baris dan sisanya dari baris alamat diumpankan ke dekoder kolom

Gambar diatas menunjukkan arsitektur SRAM asinkron 16K × 8 yang khas. Sel-sel memori diatur dalam delapan array 128 baris dan 128 kolom masing-masing. Kenangan dengan decoder alamat tunggal dirujuk

Interval waktu berbeda yang ditunjukkan dalam diagram didefinisikan sebagai berikut:

• Lengkap baca waktu siklus tRC . Ini didefinisikan sebagai interval waktu di mana kode alamat yang valid diterapkan ke baris alamat selama operasi 'baca'.

• Waktu akses RAM tACC . Ini didefinisikan sebagai selang waktu antara penerapan input alamat baru dan tampilan data output yang valid.

• Chip memungkinkan waktu akses tCO . Ini didefinisikan sebagai waktu yang diambil oleh output RAM untuk beralih dari status Hi-Z ke level data yang valid setelah CS diaktifkan.

• Chip menonaktifkan waktu akses tOD . Ini didefinisikan sebagai waktu yang diambil oleh RAM untuk kembali ke status Hi-Z setelah CS dinonaktifkan.

• Lengkapi waktu siklus tulis tWC . Ini didefinisikan sebagai interval waktu di mana kode alamat yang valid diterapkan ke baris alamat selama operasi 'tulis'. • Tulis lebar pulsa tW . Ini adalah waktu di mana R / W diadakan RENDAH selama operasi 'tulis'. • Waktu penyiapan alamat tAS. Ini adalah interval waktu antara tampilan alamat baru dan R / W yang RENDAH. • Waktu pengaturan data tDS . Ini didefinisikan sebagai interval waktu di mana R / W harus tetap RENDAH setelah data yang valid diterapkan pada input data. • Waktu penyimpanan data tDH . Ini didefinisikan sebagai interval waktu di mana data input yang valid harus tetap pada jalur data setelah input R / W menjadi TINGGI. • Alamat ditahan interval waktu tah . Ini didefinisikan sebagai interval waktu di mana alamat yang valid harus tetap pada baris alamat setelah input R / W menjadi TINGGI.

menjadi ingatan dua dimensi, dan ingatan dengan dua dekoder disebut sebagai ingatan tiga dimensi. gambar (a) dan (b) masing-masing menunjukkan diagram waktu selama operasi 'baca' dan 'tulis'. Diagramnya cukup jelas. Baca dan tulis interval waktu siklus beberapa nanodetik hingga beberapa puluh nanodetik biasa terjadi dalam kasus SRAM asinkron.

SRAM Sinkron

SRAM sinkron, seperti yang disebutkan sebelumnya, disinkronkan dengan jam sistem. Dalam hal sistem komputer beroperasi pada frekuensi clock yang sama dengan mikroprosesor. Sinkronisasi mikroprosesor dan memori ini memastikan kecepatan eksekusi yang lebih cepat. Perbedaan mendasar antara arsitektur SRAMs sinkron dan asinkron adalah bahwa SRAM sinkron memanfaatkan register ter - clock untuk menyinkronkan 'alamat', R / W, CS, dan baris 'data masuk' ke jam sistem. Gambar dibawqah menunjukkan arsitektur dasar SRAM sinkron 32K × 8 dengan fitur burst. Seperti yang dapat kita lihat dari gambar, blok array memori, blok decoder alamat dan R / W dan CS adalah sama

seperti dalam kasus SRAM asinkron. Seperti disebutkan sebelumnya, sebagian besar SRAM sinkron memiliki fitur burst alamat. Dalam hal ini, ketika alamat eksternal terkunci ke register alamat, sejumlah bit alamat terendah diterapkan ke logika burst. Logika Burst terdiri dari penghitung biner dan gerbang EKSKLUSIF-ATAU. Output dari logika burst, yang pada dasarnya menghasilkan urutan alamat internal, diumpankan ke decoder bus alamat. Dalam kasus logika burst dua- bit, urutan alamat internal yang dihasilkan diberikan oleh A1A0, A1A0, A1A0, A1 A0, di mana A0 dan A1 adalah bit alamat yang diterapkan pada logika burst. Logika burst yang ditunjukkan pada Gambar. 15.9 juga merupakan logika dua-bit.

RAM Dinamis

Sel memori dalam kasus DRAM terdiri dari kapasitor dan MOSFET. Sel memiliki nilai '1' saat kapasitor diisi dan '0' saat dilepaskan. Keuntungan utama dari jenis memori ini adalah kepadatannya yang lebih tinggi, atau lebih banyak bit per paket, dibandingkan dengan SRAM. Ini karena sel memori sangat sederhana dibandingkan dengan SRAM. Juga, biaya per bit kurang dalam kasus DRAM. Kerugian dari jenis memori ini adalah kebocoran muatan yang disimpan pada kapasitor dari berbagai sel memori ketika mereka menyimpan '1'. Untuk mencegah hal ini terjadi, setiap sel memori dalam DRAM perlu dibaca secara berkala, muatannya (atau voltase) dibandingkan dengan nilai referensi dan kemudian muatan dikembalikan ke kapasitor. Proses ini dikenal sebagai 'penyegaran memori' dan dilakukan kira-kira setiap 5-10 m . Gambar dibawah menunjukkan sel memori dasar DRAM dan prinsip operasinya. MOSFET bertindak seperti sakelar. Ketika dalam mode 'tulis' (R / W = 0 , buffer input diaktifkan saat buffer output dinonaktifkan. Ketika '1' disimpan di memori, baris 'data masuk' harus dalam status TINGGI dan 'baris baris' yang sesuai juga harus dalam status TINGGI sehingga MOSFET dihidupkan. Ini menghubungkan MOSFET ke baris 'data dalam', dan ini akan mengisi kapasitor ke tingkat tegangan positif. Ketika '0' perlu untuk disimpan, baris 'data masuk' RENDAH dan kapasitor juga memperoleh level yang sama. Ketika 'baris baris' diambil ke status RENDAH, MOSFET dimatikan dan terputus dari garis bit. mengisi kapasitor. Dalam mode 'baca' (R / W = 1 , buffer output diaktifkan ketika buffer input dinonaktifkan. Ketika 'baris baris' diambil ke logika TINGGI, MOSFET dihidupkan dan menghubungkan kapasitor. ke baris 'data out' melalui buffer output . Operasi refresh dilakukan dengan mengatur R / W = 1 dan dengan mengaktifkan buffer refresh. Ada dua basi mode c menyegarkan memori, yaitu mode burst refresh dan mode refresh terdistribusi. Dalam mode burst refresh, semua baris dalam array memori di-refresh secara berurutan selama siklus burst burst. Dalam mode refresh terdistribusi, setiap baris di-refresh pada interval yang bersinggungan antara operasi 'baca' dan 'tulis'.

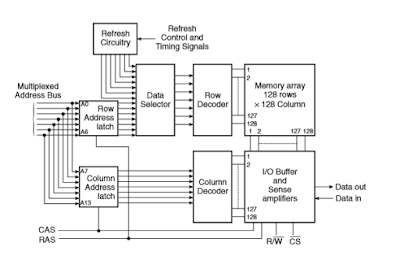

Arsitektur DRAM

Arsitektur memori DRAM agak berbeda dari memori SRAM. Baris alamat baris dan kolom biasanya multipleks dalam DRAM. Ini dilakukan untuk mengurangi jumlah pin pada paket. Pilih alamat baris (RAS) dan input pilih alamat kolom (CAS) digunakan untuk menunjukkan apakah baris atau kolom harus ditangani. Multiplexing alamat sangat menarik untuk DRAM berkapasitas lebih tinggi. RAM 4 MB, misalnya, akan membutuhkan 22 input alamat (222 = 4M)Gambar 1 menunjukkan arsitektur DRAM 16K × 1. Jantung DRAM adalah array sel memori singlebit . Setiap sel memiliki posisi unik dalam hal baris dan kolom. Blok penting lainnya termasuk decoder alamat (dekoder baris dan dekoder kolom) dan kontrol penyegaran dan kait alamat (kait alamat baris dan kait alamat kolom). Seperti yang dapat dilihat dari gambar, tujuh baris alamat adalah multiplexing waktu pada awal siklus memori oleh garis RAS dan CAS. Pertama, alamat tujuh-bit (A0-A6 terkunci ke kait alamat baris, dan kemudian alamat tujuh-bit diikat ke kait alamat kolom (A7-A13 . Mereka kemudian diterjemahkan untuk memilih lokasi memori tertentu. ukuran kata dapat dicapai dengan menggabungkan lebih dari satu chip. Hal ini dibahas pada bagian berikutnya.Gambar 2 (a) dan (b) masing-masing menunjukkan diagram waktu untuk operasi baca dan tulis. DRAM relatif lebih lambat daripada SRAM. waktu akses tipikal adalah dalam kisaran 100–250 ns.

gambar 1

Jenis DRAM DRAM

memori dapat diklasifikasikan lebih lanjut sebagai DRAM mode halaman cepat (FPM), DRAM output data diperpanjang (EDO), DRAM output data diperluas (BEDO) dan DRAM sinkron (S). Dalam FPM DRAM, alamat baris hanya ditentukan satu kali untuk akses ke beberapa alamat kolom berturut-turut. Karenanya, waktu baca dan tulis berkurang. EDO DRAM mirip dengan FPM DRAM, dengan fitur tambahan bahwa siklus akses baru dapat dimulai sambil menjaga output data dari siklus sebelumnya aktif. BEDO DRAM adalah EDO DRAM dengan kemampuan burst address. Semua jenis DRAM yang dibahas sampai sekarang adalah DRAM asinkron, dan operasinya tidak disinkronkan dengan jam sistem. SDRAM, seperti namanya, adalah DRAM sinkron yang operasinya disinkronkan dengan jam sistem.

4. Gambar Rangkaian dan Prinsip Kerja [Kembali]

BASIC RAM MEMORY CELL

arsitektur khas SRAM asinkron 64 × 8. Itu mampu menyimpan 64 kata dari delapan bit masing-masing. Blok utama termasuk decoder alamat baris 6-ke-64, buffer I / O, 64 sel memori dan logika kontrol untuk operasi baca / tulis. Sel memori dalam satu baris direpresentasikan sebagai register. Setiap register adalah register delapan bit dan dapat dibaca dari serta ditulis ke dalamnya. Seperti dapat dilihat dari gambar, semua sel di dalam register yang sama berbagi baris output decoder yang sama, juga disebut sebagai 'baris baris'. Fungsi kontrol disediakan oleh input R / W (baca / tulis) dan CS (pilih chip). Input R / W dan CS juga disebut sebagai input WE (write enable) dan CE (chip enable). Baris 'input data' dan 'output data' biasanya digabungkan dengan menggunakan jalur input / output yang umum untuk menghemat jumlah pin pada paket IC. Memori dipilih dengan membuat CS = 0. Selama operasi 'baca', status pin R / W dan CS masing-masing adalah '1' dan '0', sedangkan selama operasi 'tulis' masing-masing adalah '0' dan '0'. Selama operasi 'baca' buffer input dinonaktifkan dan konten register yang dipilih muncul di output. Selama operasi 'tulis' buffer input diaktifkan dan buffer output dinonaktifkan. Isi buffer input dimuat ke register yang dipilih, data sebelumnya yang ditimpa oleh data baru. Buffer output, sedang tristate , berada dalam keadaan impedansi tinggi selama operasi penulisan. CS = 1 membatalkan pilihan chip, dan input dan output data buffer dinonaktifkan dan pergi ke keadaan impedansi tinggi. Isi memori dalam kasus ini tetap tidak terpengaruh. Input 'chip Select' sangat penting ketika lebih dari satu chip memori RAM digabungkan untuk mendapatkan kapasitas memori yang lebih besar. Dalam kasus memori SRAM yang lebih besar, ada dua decoder alamat, satu untuk baris dan satu untuk kolom. Mereka disebut sebagai decoder baris dan decoder kolom masing-masing.Beberapa baris alamat diumpankan ke dekoder baris dan sisanya dari baris alamat diumpankan ke dekoder kolom

5. Video [Kembali]6. Link download [Kembali]

rangkaian : download

data sheet - download

video - download

Tidak ada komentar:

Posting Komentar