1. Tujuan [Kembali]

Memahami rangkaian logika dengan menggunakan T (toggle) Flip flop dengan clock, sebagai operasi penghitung riak biner.

2. Alat dan bahan [Kembali]

Alat dan bahan yang digunakan yaitu :

a. Negative edge triggered J-K flip-flops

b. clock

c. Logicstate

d. Logic probe

3. Teori [Kembali]

- Negative Edge-Triggered J-K flip-flops

Pada JK flip-flop dibuat jalur balik dari masing-masing keluaran Q dan Q’ menuju gerbang masukan NAND, hal ini tidak masalah karena gerbang NAND dapat memiliki lebih dari dua masukan. Nama JK flip-flop diambil untuk membedakan dengan masukan pada SR flip-flop karena ada perubahan ada perubahan jalur balik di atas. Secara umum cara kerja JK flip-flop sama dengan SR flip-flop. Perbedaannya pada saat JK bernilai 1 1 yang menyebabkan kondisi keluaran berubah (1 ke 0 dan 0 ke 1) atau toggle.

JK flip-flop memiliki 2 masukan yang biasanya ditandai dengan huruf J dan K. Jika J dan K berbeda maka keluaran Q akan sama dengan nilai J pada clock berikutnya (next clock). Jika J dan K keduanya 0 maka tidak terjadi perubahan apa-apa pada flip-flop. Jika J dan K keduanya 1 maka kondisi Q akan berubah dari kondisi sebelumnya, Jika sebelumnya Q bernilai 0 maka akan bernilai 1 dan sebaliknya. Karakter JK flip-flop yang lebih pasti untuk semua kondisi maka flip-flop ini yang banyak digunakan untuk membangun berbagai komponen register seperti: register geser (shift register), pencacah biner (binary counter), pendeteksian sekuensial (sequence detector) dan lain-lain.

Pada saat clock naik/bernilai 1 maka kondisi keluaran Q ditentukan oleh masukan JK. Kondisi Set (keluaran bernilai 1) tercapai pada saat JK bernilai 10. Kondisi Reset (keluaran bernilai 1) tercapai pada saat JK bernilai 01. Pada flip flop JK tidak ada lagi kondisi pacu seperti pada flip-flop SR. Pada saat JK bernilai 11 maka nilai keluaran Q akan berubah-ubah (toggle) pada saat setiap clock -nya.

tabel kebenaran JK Flip flop

2. Clock (detak)

lock yaitu pulsa-pulsa periodik yang biasanya berbentuk bujur sangkar (duty cycle 50%), seperti yang ditunjukkan pada gambar 16. SR Flip-Flop bekerja secara asinkron. Nilai S dan R dapat berubah kapan saja dan dalam tempo yang tidak bersamaan. Detak (clock) ditambahkan pada sisi masukan untuk menjaga sinyal agar bekerja dalam tenggang tempo yang bersamaan. Operasi-operasi yang terjadi di dalam sistem digital sinkron terjadi pada waktu-waktu pulsa clock bertransisi dari 0 ke 1 atau dari 1 ke 0. Waktu-waktu transisi ini ditunjukkan pada gambar 16. Transisi 0 ke 1 disebut sisi naik (rising edge) atau sisi menuju positif, transisi dari 1-ke-0 disebut sisi jatuh (falling edge) atau sisi menuju negatif. Kendali ini membantu flip-flop lebih stabil. Clock ditambahkan sebelum sinyal S dan R masuk ke dalam rangkaian flip-flop. Masing-masing sinyal masukan di NAND-kan dengan clock. Pada saat clock bernilai 0, tidak ada perubahan sinyal yang masuk ke dalam flip-flop.

3. Logicstate

untuk memberikan nilai logika 1 atau 0

4. Logicprobe

untuk menampilkan nilai keluaran, yang nilainya 0 atau 1.

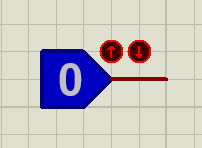

4. Gambar Rangkaian dan Prinsip Kerja [Kembali]

Prinsip kerja :

Rangkaian akan aktif ketika logika input adalah 1. Ketika logika input 1 maka fungsi penghitung sebagai berikut. Mari kita asumsikan bahwa semua flip flop pada awalnya dihapus ke kondisi '0'. Pada transisi TINGGI ke RENDAH dari pulsa jam pertama, Q0 beralih dari ‘0’ ke ‘1 ow karena tindakan bergantian. Karena flip flop yang digunakan adalah yang dipicu oleh negatif edge, transisi '0' ke '1' pada Q0 tidak memicu flip-flop FF1. FF1, bersama dengan FF2 dan FF3, tetap dalam kondisi '0'. Jadi, pada terjadinya transisi clock negative-going pertama, Q0 = 1, Q1 = 0, Q2 = 0 dan Q3 = 0. Pada transisi TINGGI ke RENDAH dari pulsa clock kedua, Q0 beralih lagi. Artinya, mulai dari ‘1’ hingga ‘0’. Transisi '1' ke '0' pada output Q0 memicu FF1, output Q1 yang berasal dari '0' ke ‘1’. Output Q2 dan Q3 tetap tidak terpengaruh. Oleh karena itu, segera setelah terjadinya transisi TINGGI ke RENDAH kedua dari sinyal clock, Q0 = 0, Q1 = 1, Q2 = 0 dan Q3 = 0. Pada baris yang sama, kita dapat menjelaskan status logika Q0, Q1 , Output Q2 dan Q3 segera setelah transisi jam berikutnya. Status logika output untuk 16 pertama transisi sinyal jam relevan (TINGGI ke RENDAH) dirangkum dalam Tabel 11.1. Dengan demikian, kita melihat bahwa penghitung melewati 16 keadaan yang berbeda dari 0000 ke 1111 dan kemudian, pada terjadinya transisi yang diinginkan dari pulsa clock keenambelas, ia me-reset ke keadaan asli 0000 dari tempat dimulainya. Hal ini sesuai dengan tabel kebenaran.

5. Video [Kembali]

6. Link download [Kembali]

Video : download

rangkaian : download

data sheet : download

Tidak ada komentar:

Posting Komentar